# High Performance Buffer Amplifier for Liquid Crystal Display System

Arun Kumar\*, Prof. Tarun Varma\*\* and Dr. Rita Jain\*\*\*

\*PG Scholar, Department of Electronics and Communication Engineering, LNCT, Bhopal, (MP) India \*\*Assistant Prof., Department of Electronics and Communication Engineering, LNCT, Bhopal, (MP) India \*\*Prof. & HOD, Department of Electronics and Communication Engineering, LNCT, Bhopal, (MP) India

> (Corresponding author: Arun Kumar) (Received 05 July, 2014 Accepted 28 August, 2014)

ABSTRACT: A high performance and buffer amplifier for liquid crystal display system is presented here. The proposed architecture contains self biased RAIL TO RAIL complementary differential pair , and class B output driving stage which is suitable for large and small size liquid crystal display, compensation capacitor and resistance are used to improve the settling time and slew rate of the buffer amplifier, an experimental prototype is shown here which is implemented in a .35  $\mu m$  CMOS technology which draws only 8  $\mu m$  static current and provide a settling time of 2.8  $\mu s$  and rising and 3  $\mu s$  during four the act area for the design of the buffer is 49 \*60  $\mu m$  With power supply of 3.3 it with stand with 1000 pF load capacitance.

# I. INTRODUCTION

With incrementing ordinant dictation of high-speed high quality liquid crystal exhibit and market in recent years we have to match with these requisites to consummate the market demand and LCD driver generally contains shift registers, input register's, data latch, level shifter, digital to analog converter, Pre-Emphasis, and analog buffers the output buffer amplifier is vigorously affects the speed, resolution, voltage swing and power dissipation [12,4,8.9]. For each pixel we require a buffer amplifier so as the number of pixel increases the number of buffers to drive the to drive the panel increases, nowadays battery operated portable contrivances are acclimated to increment the performance and to elongate the battery life we require low-power high-speed buffer amplifier. LCD output buffer amplifier are realized by operational amplifier in unity gain configuration generally RAIL TO RAIL operational amplifiers are acclimated to get plenary output swing RAIL TO RAIL operation amplifiers are consist of complimentary differential amplifiers at first stage and a summing current source at second is stage with generally kenned as folded cascoded architecture then the output is stage which are this work in class B and class AB.

### II. PROPOSED BUFFER DRIVING SCHEME

Generally introducing zero in transfer function of buffer amplifier using phase compensation register and output it makes the buffer stable but the slew rate is limited as due to small slew rate the settling time for large capacitive load will increased, means we have to suffer to achieve high-speed. A typical two stage operational amplifier requires compensation for the stability some buffer amplifier's takes the output node as the dominant to achieve the stability without Miller capacitance [3,6] however charge conservation technique is commonly used in some LCD driver to reduce the dynamic power dissipation [1,2].

ISSN No. (Online): 2277-2626

# III. ZERO COMPENSATION TECHNIQUE

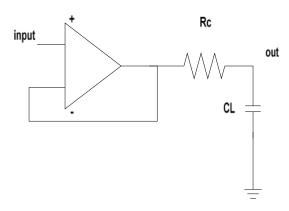

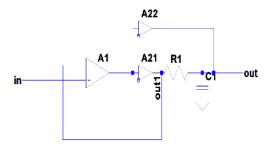

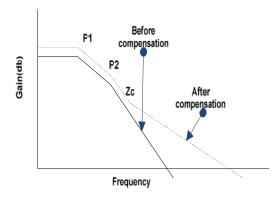

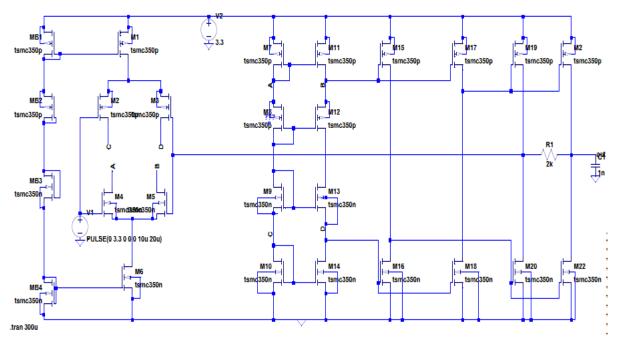

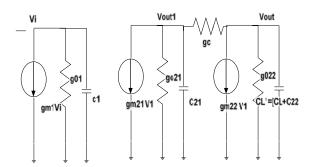

Zero compensation technique is generally used to get the dominant pole in buffer amplifier figure 1 shows a buffer amplifier with zero compensation. And fig 2 shows the configuration of proposed buffer amplifier using zero compensation technique. Fig. 4 shows the schematic of proposed buffer amplifier.

Fig. 1. Zero compensation buffer amplifier.

Fig. 2. Configuration of proposed driving method of buffer.

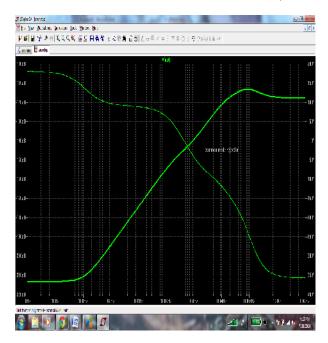

Fig. 3. Frequency response of buffer amplifier with dominant.

In figure 3 solid line shows frequency characteristic before compensation and dotted line after compensation, As dominant pole P1 shifted towards origin as with increasing load capacitance means gain bandwidth will decrease it also makes system unstable and degrade phase margin, for proper operation of buffer for high speed phase margin should be in between  $70^{\circ}$  to  $45^{\circ}$  generally they prefer  $60^{\circ}$  phase margin for high speed low-power buffer amplifier design here using " $R_{\mathcal{L}}C_{\mathcal{L}}$ " introduces required phase margin, it introduce a zero in transfer function.

$$Z_C = \frac{-1}{R_C C_L}$$

This is called as zero compensation technique for large phase margin, it is generally used when we does not use them Miller capacitor in between differential amplifier and output is stage of differentiated amplifier. The value of zero located to left the most of unity gain bandwidth to the college RGB

$$\zeta = R_C \sqrt{C_L}$$

For 70° phase and margin **≥ 1** and amplifier is stable, for < .6 the phase margin is approximately given as I moved to women in

$$PM \approx 100 \times \zeta$$

and settling time =  $\frac{4}{\zeta \omega_n}$

To get large phase margin  $R_C$  should be large but we can't increase the resistance  $R_C$  so much as it decreases the settling time, so there is compromise in between phase margin and settling time to get optimum phase margin.

As to account large capacitive load we have to increase the biasing current but it will increase the power loss in buffer amplifier, to solve on the issue to account the large capacitive load current dynamic current sensing technique is used to provide extra biasing current only during transition of input signal with the help of voltage divider method the current sensing technique sense the falling and rising edge according to that it provide the extra biasing current.

Fig. 4. Schematic of proposed buffer amplifier.

# IV. SMALL SIGNAL ANALYSIS OF PROPOSED

**Fig. 5.** Small signal model of proposed buffer.

The small signal of the proposed driving scheme is shown in figure 5 when we does not count the the transconductance of complimentary differential pair is gm1, and gm21, gm22 are the transconductance of two competitors, and g01, g021 and g022 are the output conductance, and  $C_1$ ,  $C_2$ , and  $C_2$ , are the paracetic capacitance. The open loop transfer function of the buffer,

$$A_0(s) = \frac{V_{out1}(s)}{V_i(s)} \approx A_{do} \frac{\left(1 - \frac{s}{Z_o}\right)}{\left(1 - \frac{s}{R_1}\right)\left(1 - \frac{s}{R_2}\right)}$$

where

$$A_{do} = \frac{g_{m1}(g_{m21}g_c + g_{m21}g_{022} + g_{m22}g_c)}{g_{01}(g_cg_{021} + g_cg_{022} + g_{021}g_{022})}$$

$$\approx \frac{g_{m1}(g_{m2} + g_{m22})}{g_{01}(g_{021} + g_{022})}$$

$$P_1 = -\frac{(g_cg_{021} + g_cg_{022} + g_{021}g_{022})}{C'_L(g_{021} + g_c)}$$

$$\approx \frac{g_{021} + g_{022}}{C'_L}$$

$$P_{\mathbf{z}} = -\frac{g_{01}}{C_{1}}$$

$$Z_{C} = -\frac{(g_{m21}g_{C} + g_{m21}g_{022} + g_{m22}g_{C})}{C'_{L}g_{m21}}$$

The above Equivalent circuit contains contains three poles and zero the third pole is far away from other poles and zero, so it is neglected, g01, g021 and g022 conductance are much smaller than gc, the parasitic capacitance is also much smaller than load capacitance these approximations are taken for the analysis.

The closed loop transfer functiom of buffer,

$$A_{c1}(S) = \left(\frac{V_{out1}(s)}{V_{i}(s)}\right)_{closed\ loop} = \frac{A_{o1}(s)}{1 + A_{o1}(s)}$$

$$\approx \frac{\left(1 - \frac{s}{Z_c}\right)}{1 - s\left(\frac{1}{AP_1} + \frac{1}{Z_c}\right) + s^2 \frac{1}{AP_1P_2}}$$

the relation between Vout1 and Vout2 from the figure 5 is expressed as:

$$\frac{V_{out}}{V_{out1}} \approx \frac{1 + S \frac{g_{m22}G_{21}}{g_{m21}g_c + g_{m22}g_c + g_{m22}g_{o21}}}{1 + S \frac{g_{m21}G_L}{g_{m21}g_c + g_{m21}g_{o22} + g_{m22}g_c}}$$

the closed loop transfer function of overall block as shown in figure 4:

$$A_{c}(S) = \left(\frac{V_{\text{out1}}(s)}{V_{i}(s)} \frac{V_{\text{out}}(s)}{V_{\text{out1}}(s)}\right)_{closed\ loov}$$

$$= \frac{1 + S \frac{g_{m22}C_{21}}{g_{m21}g_C + g_{m22}g_C + g_{m22}g_{o21}}}{1 - s\left(\frac{1}{AP_1} + \frac{1}{Z_C}\right) + s^2 \frac{1}{AP_1P_2}}$$

The zero from the data transfer function is neglected as it is far away from the dominant pole.

$$A_c(S) \approx \frac{1}{1 - s\left(\frac{1}{AP_1} + \frac{1}{Z_c}\right) + s^2 \frac{1}{AP_1P_2}}$$

and it is equivalent to second o order transfer function so,

$$\begin{split} & \omega_m = \sqrt{A_{dc} P_1 P_2} \\ & \zeta = -\frac{1}{2} \sqrt{A_{dc} P_1 P_2} \left( \frac{1}{A_{dc} P_1} + \frac{1}{Z_c} \right) \\ & \zeta \approx \frac{g_{m21} R_c}{2} \sqrt{\frac{g_{m1} C_L}{(g_{m21} + g_{m22}) C_1}} \end{split}$$

As from the above expressions damping factor depends upon transconductance gm1, and the resistance of MOS using the push-pull output is stage depends upon the current flowing and push-pull stage With the use of dynamic bias sensor, we increase the biasing current during the transition phase of input this results in increase of transconductance gm1 and decreasing output resistance of push-pull stage during charging and discharging with load capacitance, as the settling time depends upon damping factor and natural frequency both this parameters increases with increasing transconductance of gm1 where gm1 is transconductance of differential is stage, this results and decreasing the settling time means the response of buffer amplifier increases with the use of dynamic bias sensor.

# V. DESIGN PARAMETERS OF RAIL-RAIL OPERATIONAL AMPLIFIER

| process                 | .35 μm CMOS technology |

|-------------------------|------------------------|

| Power supply            | 3.3 V                  |

| Load resistance         | 20 k                   |

| Load capacitance        | 1000 pF                |

| power dissipation       | 1mW                    |

| DC gain                 | 95 db                  |

| Gain bandwidth product  | 1 MH                   |

| Phase margin            | 70°                    |

| Slew rate               | 5 V/ μs                |

| Output voltage swing    | 0-3.3 V                |

| input common mode range | 0-3.3 V                |

| Output stage            | Class B                |

#### VI. SIMULATION RESULT

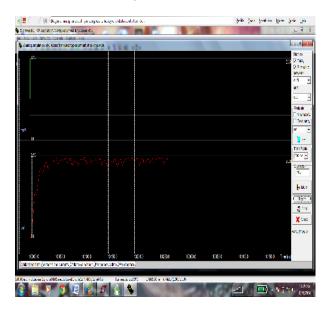

Fig. 6. Simulation result for step response.

Fig. 7. Simulation result for triangular response.

**Fig. 8.** Current at trail end of PMOS & NMOS differential pair.

**Fig. 9.** Power consumption differential pair during static condition.

**Fig. 10.** Static current in biasing network and differential pair.

**Fig. 11.** Simulation result of common mode rejection ratio.

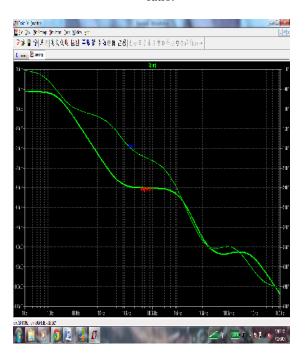

**Fig. 12.** Frequency response of proposed buffer amplifier.

**Fig. 13.** Simulation result of Input common mode range.

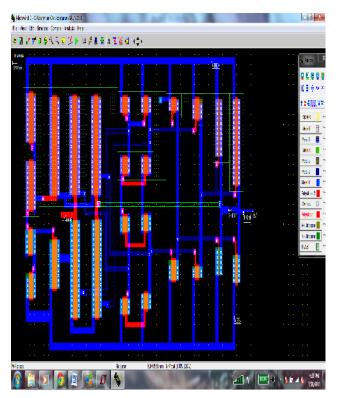

**Fig. 14.** Layout diagram of rail to rail differential amplifier.

Fig. 15. Simulation result of rail to rail differential amplifier for step response.

# VII. COMPARISON TABLE

|             | Ref.[20]     | Ref.[3]      | <b>Ref.[4]</b> | <b>Ref.</b> [1] | This         |

|-------------|--------------|--------------|----------------|-----------------|--------------|

|             |              |              |                |                 | work         |

|             |              |              |                |                 | is           |

| CMOS        | .6 µm        | .6 µm        | .6 µm          | .5 µm           | .35          |

| technology  |              |              |                |                 | μm           |

| G 1         | <b>= T</b> 7 | <b>= T</b> 7 | = ×7           | <b>= T</b> 7    | 22.77        |

| Supply      | 5 V          | 5 V          | 5 V            | 5 V             | .33 V        |

| voltage     |              |              |                |                 |              |

| Max load    | 680 pF       | 170 pF       | 30 pF          | 1000            | 1000         |

| capacitor   |              |              |                | рF              | рF           |

|             |              |              |                | P               | P-           |

| Quiescent   | 30 μΑ        | 5 μΑ         | 8.2 μΑ         | 32 μΑ           | 8 μΑ         |

| current     |              |              |                |                 |              |

| Settling    | 1.2 μs       | 9.6 µs       | 8.2 μs         | .7 μs           | 3.2          |

| time        |              |              |                |                 |              |

|             |              |              |                |                 | μs           |

| Input-      | .15/4 V      | .15/4.8      | .5/4.5         | 0/5 V           | 0/3.2        |

| output      |              | $\mathbf{v}$ | <b>T</b> 7     |                 | $\mathbf{v}$ |

| range [V]   |              | V            | $\mathbf{V}$   |                 | V            |

| Input-      | 77%          | 93%          | 80%            | 100 %           | 97           |

| output      |              |              |                |                 | %            |

| range       |              |              |                |                 | 70           |

| [VDD%]      |              |              |                |                 |              |

| Slew rate   | =            | _            | _              | _               | 7 V /        |

|             |              |              |                |                 | μs           |

|             |              |              |                |                 | MB           |

| Active area | N/A          | N/A          | N/A            | 73 ×            | 50           |

| [µm²]       |              |              |                | 91              | ×60          |

|             |              |              |                |                 |              |

# VIII. CONCLUSION

Self biased high-speed low-power rail to rail buffer amplifier for LCD is proposed work under class B operation which is suitable for small and large size LCD panel, the Zero compensation is used to enhance the slew rate and settling time the compensation resistor value should be optimized to get the optimal value of slew rate and phase margin, as with large value of compensation resistor we get adequate phase margin but it will increase settling time and vice versa. A prototype of this buffer is implemented on 0.35 µm CMOS technology it draws only is 8 µA static current. The buffer draws little static current but has a large driving capability during transition phase, full swing is obtained by RAIL TO RAIL operational amplifier and enlarge driving capability is obtained by the use of two comparators. The buffer is 3 µs of rising settling time and 3.2 µs of falling settling time, the active area occupied by the buffer is approximately 3600 µm<sup>2</sup>. The performance of the proposed buffer is compared with previous buffer it is superior in power consumption, low static current and small settling time.

# REFERENCES

- [1]. Alfio Dario Grasso, *Member, IEEE*, Davide Marano, Fermin Esparza-Alfaro, Antonio J. Lopez-Martin, *Senior Member, IEEE*, Gaetano Palumbo, *Fellow, IEEE*, "Self-Biased Dual-Path Push-Pull Output Buffer Amplifier for LCD Column Drivers" *IEEE transactions on circuits and systems—i: regular papers*, vol. **61**, no. 3, march 2014

- [2]. D.J.R. Cristaldi, S. Pennisi, and F. Pulvirenti, Liquid Crystal Display Drivers: Techniques and Circuits. New York: Springer, 2009.

- [3]. M.C. Weng and J.C. Wu, "A compact low-power Rail-to-Rail class-B buffer for LCD column driver," *IEICE Trans. Electron.*, vol. **E85-C**, no. 8, pp. 1659–1663, Aug. 2002.

- [4]. T. Itakura and H. Minamizaki, "A two-gain-stage amplifier without an on-chip Miller capacitor in an LCD driver IC," *IEICE Trans. Fundam.*, vol. **E85-A**, no. 8, pp. 1913–1920, Aug. 2002.

- [5]. C.-W. Lu, "High-speed driving scheme and compact high-speed low-power Rail-to-Rail class-B buffer amplifier for LCD applications," *IEEE J. Solid-State Circuits*, vol. **39**, pp. 1938–1947, Nov. 2004.

- [6]. C.W. Lu, C.M. Hsiao, and P.Y. Yin, "Voltage selector ad a linearity enhanced DAC-embedded opamp for LCD column driver ICs," *IEEE J. Solid-State Circuits*, vol. **48**, pp. 1475–1486, Jun. 2013.

- [7]. J. Ramirez-Angulo, A. Torralba, R.G. Carvajal, and J. Tombs, "Low-voltage CMOS operational amplifiers with wide input-output swing based on a novel scheme," *IEEE Trans. Circuits Syst. I, Fundam. Theory Appl.*, vol. **47**, no. 5, pp. 772–774, May 2000.

- [8]. S. Karthikeyan, S. Mortezapour, A. Tammineedi, and E.K.F. Lee, "Low-voltage analog circuit design based on biased inverting opamp configuration," *IEEE Trans. Circuits Syst. II, Analog Digit. Signal Process.*, vol. **47**, no. 3, pp. 176–184, Mar. 2000.

- [9]. G. A. Rincon-Mora and R. Stair, "A low-voltage, rail-to-rail, class-AB CMOS amplifier with high drive and low output impedance characteristics,"

- IEEE Trans. Circuits Syst. II, Analog Digit. Signal Process., vol. 48, no. 8, pp. 753–761, Aug. 2001.

- [10]. K. J. de Langen and J. H. Huijsing, "Compact low-voltage power-efficient operational amplifier cells for VLSI," *IEEE J. Solid-State Circuits*, vol. **33**, no. 10, pp. 1482–1496, Oct. 1998.

- [11]. A. Torralba, R.G. Carvajal, J. Ramirez-Angulo, J. Tombs, and J. Galan, "Class AB output stages for low voltage CMOS opamps with accurate quiescent current control by means of dynamic biasing," in *Proc. IEEE ICECS'01*, Sep. 2001, vol. **2**, pp. 967–970.

- [12]. F. You, S. H. K. Embabi, and E. Sánchez-Sinencio, "Low-voltage class AB buffers with quiescent current control," *IEEE J. Solid-State Circuits*, vol. **33**, no. 6, pp. 915–920, Jun. 1998.

- [13]. G. Palmisano and G. Palumbo, "Very efficient CMOS low-voltageoutput stage," *Electron. Lett.*, vol. 31, no. 21, pp. 1830–1831, Oct. 1995.

- [14]. T. Stockstad and H. Yoshizawa, "A 0.9-V 0.5-A rail-to-rail CMOS operational amplifier," *IEEE J. Solid-State Circuits*, vol. **37**, no. 3, pp. 286–292, Mar. 2002.

- [15]. W. Aloisi, G. Giustolisi, and G. Palumbo, "A 1-V CMOS output stage with excellent linearity," *Electron. Lett.*, vol. **38**, no. 22, pp. 1299–1300, Oct. 2002.

- [16]. R. van Dongen and V. Rikkink, "A 1.5 V class AB CMOS buffer amplifier for driving low-resistance loads," *IEEE J. Solid-State Circuits*, vol. **30**, no. 12, pp. 1333–1338, Dec. 1995.

- [17]. G. Palumbo, "1.2V CMOS output stage with improved drive capability," *Electron. Lett.*, vol. **35**, no. 5, pp. 358–359, Mar. 1999.

- [18]. G. Palmisano, G. Palumbo, and R. Salerno, "A 1.5-V high drive capability CMOS Op-Amp," *IEEE J. Solid-State Circuits*, vol. **34**, no. 2, pp. 248–252, Feb. 1999.

- [19]. P.C. Yu and J.C. Wu, "A class-B output buffer for flat-panel-display column driver," *IEEE J. Solid-State Circuits*, vol. **34**, pp. 116–119, Jan. 1999.

- [20]. C.W. Lu and C.L. Lee, "A low-power high-speed class-AB buffer amplifier for flat-panel-display application," *IEEE Trans. Very Large Scale Integr.* (VLSI) Syst., vol. **10**, pp. 163–168, Apr. 2002.

- [21]. C.W. Lu and P.H. Xiao, "A high-speed low-power Rail-to-Rail buffer amplifier for LCD application," in *Proc. CCECE*, Dec. 2006, pp. 709–712.

- [22]. J.H. Wang, J.C. Qiu, H.Y. Zheng, C.H. Tsai, C.Y. Wang, C.C. Lee, and C.T. Chang, "A compact low-power high slew-rate Rail-to-Rail class-AB buffer amplifier for LCD driver ICs," in *Proc. EDSSC*, Dec. 2007, pp. 397–400.

- [23]. W.-J. Huang, S. Nagayasu, and S.I. Liu, "A Rail-to-Rail class-B buffer with DC level-shifting current mirror and distributed Miller compensation

- for LCD column drivers," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. **58**, no. 8, pp. 1761–1772, Aug. 2011.

- [24]. D. Marano, G. Palumbo, and S. Pennisi, "Low-power high-speed Rail-to-Rail LCD output buffer with dual-path push-pull operation and

- quiescent current control," *Analog Integr. Circuits Signal Process*, vol. **65**, no. 2, pp. 289–298, Sep. 2010. [25]. W. Aloisi, G. Giustolisi, and G. Palumbo, "Design and comparison of very low-voltage CMOS output stages," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. **52**, no. 8, pp. 1545–1556, Aug. 2005.